- MMU 概念

- 虚拟地址转换为物理地址

- Cache 概念

名词解释

- VA 虚拟地址

- PA 物理地址

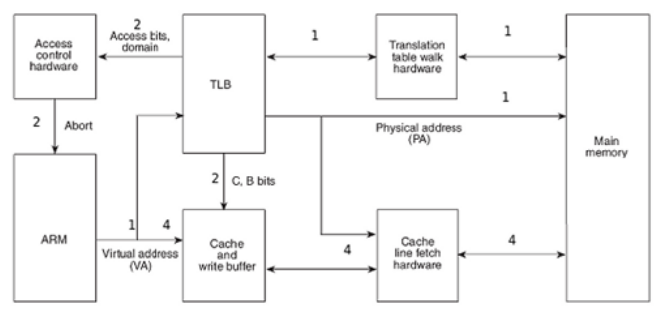

- MMU 内存管理单元,是硬件设备,用于完成地址映射

- TLB 是 MMU 的一部分,是一块高速缓存,用于缓存页表,提高页表查询速度

- 页表 是内存管理系统中的数据结构,保存 VA 到 PA 的映射,位于主内存中,相对于 CPU,属于慢速设备

- Cache 是硬件设备,为了解决处理器与慢速 DRAM(慢速 DRAM 即内存)设备之间巨大的速度差异

- cacheline,cache 分成多个组,每个组分成多个行,linesize 是 cache 的基本单位,从主存向 cache 迁移数据都是按照 cacheline 为单位替换

- page 页,一般为 4k

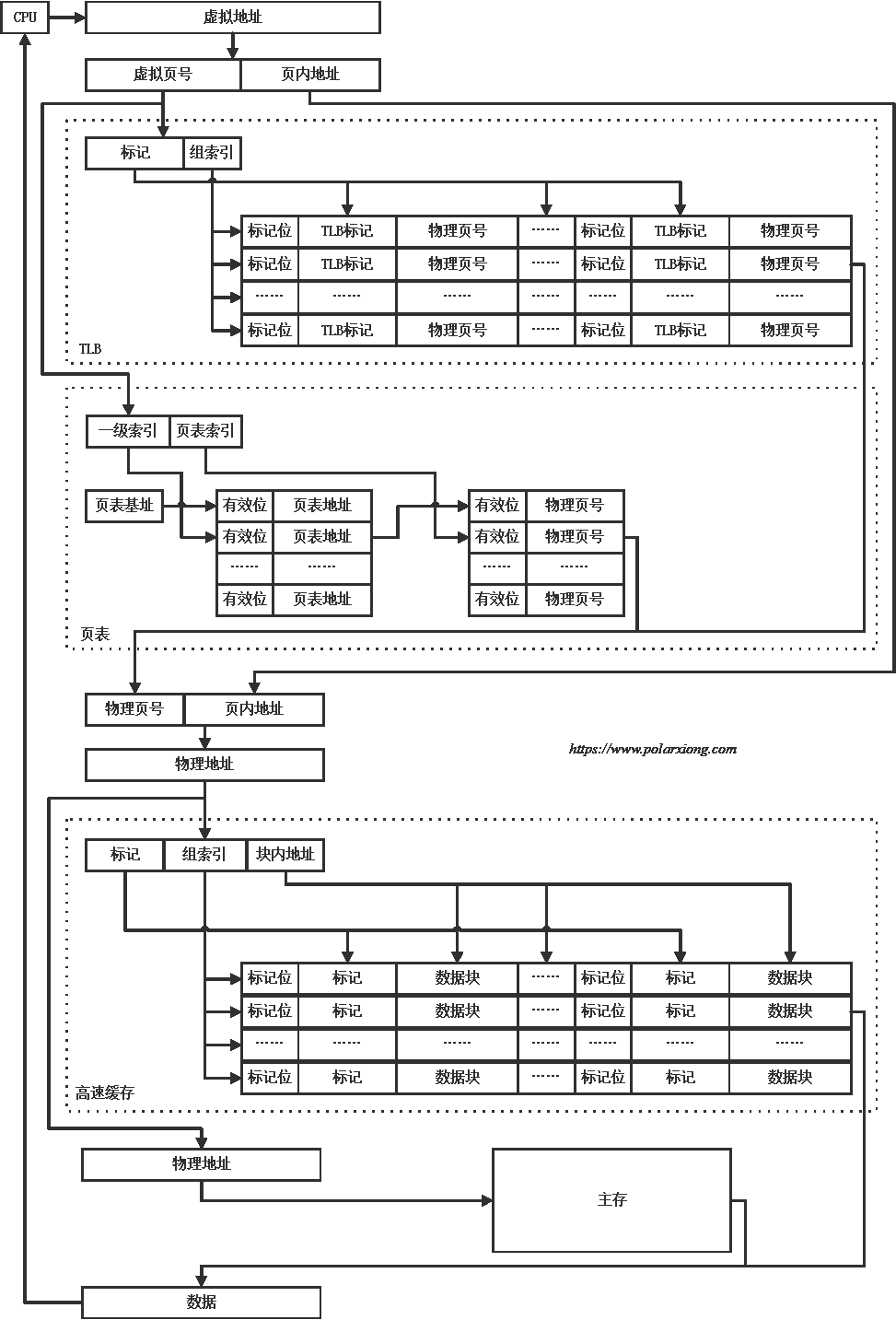

page 是 os 的概念,而 cache 是 cpu 的概念。虚拟地址和物理地址以 page 为单位进行操作的,由两部分组成:page 地址和 page 内地址

虚拟内存

虚拟地址 VA 到物理地址 PA 以页 page 为单位。通常 page 的大小为 4K。物理页面称为 page frame。

虚拟地址到物理地址是一个查表的过程,但可能不只一个表,是一个多级的表。虚拟地址本身分为几个部分,page 地址和 page 内地址,page 地址分为多级用于查表。这个过程称为 Translation Table Walk,由硬件完成。上述所指的表,是保存在内存上的。

MMU 包括 TLB 和 Translation Table Walk,TLB(Translation Lookaside Buffer)是一块高速缓存,缓存最近查找过的 VA 对应的页表项。如果 TLB 中有需要查表的 VA,就不用 Translation Table Walk 了,Translation Table Walk 较慢要从内存上读表。

Cache

Cache 设计:

- 组相联

- 全相联

- 直接映射

Cache 写回内存模式:

- Write Back

- Write Through

VA2PA

- TLB采用组相联

- 页表采用两级页表

- cache采用组相联,仅考虑L1 d-cache,不考虑L1 i-cache、L2 cache和L3 cache

- 未考虑页表缺页

- 简化了cache未命中情况